Orman Yangınlarına ‘Kule’ Müdahalesi

İzmir Ekonomi Üniversitesi’nde (İEÜ) görev yapan Prof. Dr. Celalettin Kozanoğlu ve Prof. Dr. Murat Aşkar, orman yangınlarının en kısa sürede ...

Hayat Kurtaracak Projeler

İzmir Ekonomi Üniversitesi (İEÜ) öğrencileri, ülkemizde deprem, sel ve yangın gibi doğal afetlerin artması üzerine harekete geçerek arama ve kurtarma ...

İzmir Ekonomili Profesöre 'Başkanlık' Görevi

Stanford Üniversitesi’nden özel bir araştırma ekibinin açıkladığı ‘Dünyanın En Etkili Bilim İnsanları Listesi’nde yer alan İzmir Ekonomi Üniversitesi (İEÜ) Elektrik-Elektronik ...

İzmir Ekonomi’de ‘Dörtlü Gurur’

Amerika Birleşik Devletleri’ndeki (ABD) Stanford Üniversitesi’nden Dr. John loannidis’in liderliğinde çalışan özel bir araştırma ekibinin açıkladığı ‘Dünyanın En Etkili Bilim ...

Avrupa’nın 132 Kişilik Başarı Listesine Girdi

İzmir Ekonomi Üniversitesi’nden (İEÜ) Doç. Dr. Pınar Oğuz Ekim, büyük şirketlerin tedarik merkezlerinde, depolarında ya da fabrikalarında kullanılması amacıyla geliştirdiği ...

Akıllı Robotlar Türkiye İkincisi

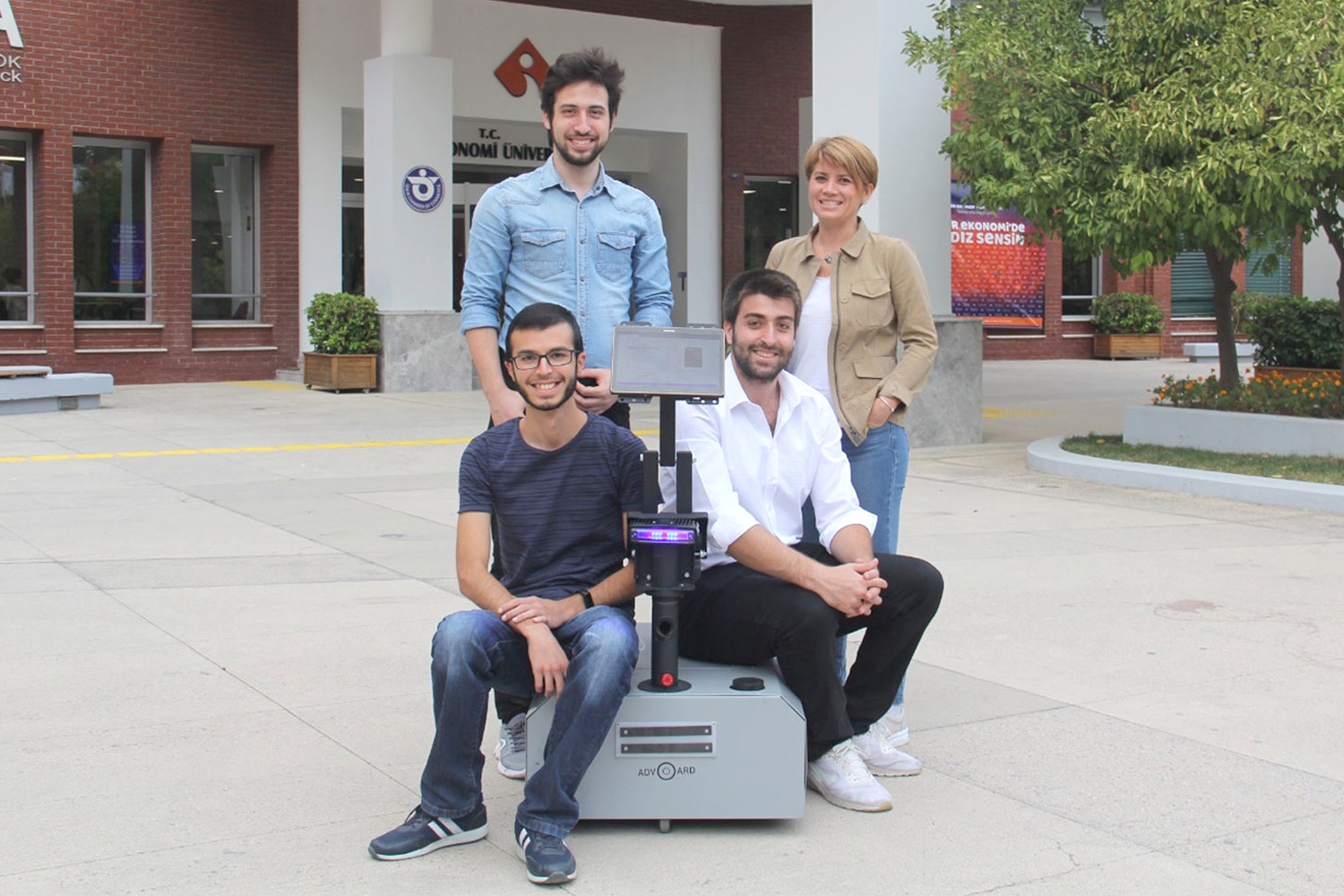

İzmir Ekonomi Üniversitesi (İEÜ) Öğretim Üyesi Doç. Dr. Pınar Oğuz Ekim, 3 öğrencisiyle birlikte geliştirdiği ‘otonom taşıma yapan robotlarla’ Başakşehir ...

Dünyanın En Etkili Bilim İnsanları Arasına Girdiler

Amerika Birleşik Devletleri’ndeki (ABD) Stanford Üniversitesi’nden Dr. John loannidis’in liderliğinde çalışan özel bir araştırma ekibinin açıkladığı ‘Dünyanın En Etkili Bilim ...

‘Robot’la Paris yolcusu

İzmir Ekonomi Üniversitesi’nde (İEÜ) görev yapan Doç. Dr. Pınar Oğuz Ekim, 3 öğrencisi ile birlikte kurduğu ‘Advoard Robotics' adlı teknoloji ...